## Orange Tree Technologies

### **ZestETM1 Datasheet**

### **ZestETM1: Gigabit Ethernet TOE Module**

Gigabit Ethernet hardware TCP/IP Offload Engine and embedded device server that delivers a data rate of over 100MBytes/s in each direction and a flexible interface to external user devices.

The ZestETM1 is a low cost, easy to use, very high performance TCP/IP offload Engine (TOE) that provides a simple bridge between a high speed network and an embedded device client or server. It sustains a data rate of 100MBytes/s in each direction and can be used for existing and new product designs.

With its low power consumption (<1.5W) and compact form factor (25mm x 30mm), the module is ideally suited to integration in embedded systems and OEM equipment. It has support for real-time applications in Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE). PTP synchronises devices on the network to a central time source device so that they can trigger operations at the same time and capture timestamped events. SyncE enables each network device to generate a 125MHz clock synchronised across the network. These are protocols that run over Ethernet and therefore require no extra interconnect.

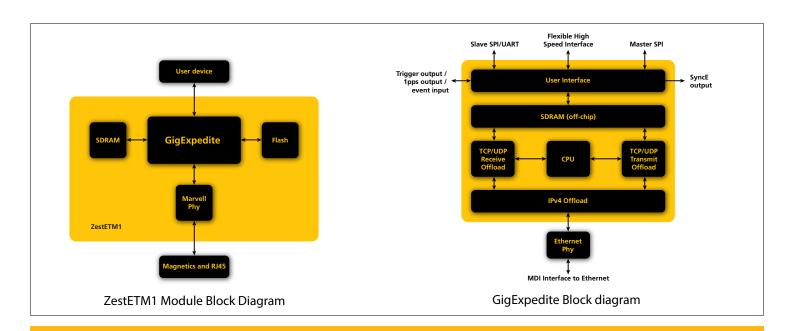

Fitted onto the ZestETM1 module is Orange Tree's second generation GigExpedite (GigEx) chip that delivers hardware UDP and TCP/IP Offload (TOE),

10/100/1000 Ethernet, an Ethernet MAC and embedded web server.

The ZestETM1's GigEx device supports IPv4, UDP and TCP transport layer protocols as a complete networking solution or as a foundation for implementing specialized higher level protocols in the connected device.

The GigEx integrated hardware TCP/IP stack including hardware UDP and TCP/IP Offload Engine (TOE) removes the network protocol processing burden from the companion processor or FPGA. Resource-intensive memory copies, checksum computation, reassembling of out-of-order packets and data acknowledgement and retransmission are handled by the GigEx hardware TOE simplifying data transfer to the connected device to a FIFO-like stream.

The second generation of Orange Tree's GigEx chip provides multiple and varied interfaces including standard SPI master and slave and high speed UART buses alongside a configurable high speed parallel interface. Full control of the GigEx device is possible via the low speed serial interfaces leaving the high speed parallel interface for data transfer. This allows a smaller, lower cost CPU or microcontroller to be deployed in the system outside the high speed data path, and glueless high speed data connection to FPGAs, DACs, ADCs, bus transceivers or other devices.

Orange Tree Technologies Ltd

The board-level embedded hardware and software solutions company

Tel +44 1235 838646 Email: info@orangetreetech.com

© Copyright 2013 Orange Tree Technologies

# Comparison of traditional software stack running on a microprocessor with GigExpedite

| Feature                                          | Software Stack                                                                          | ZestETM1 GigExpedite™                                                                                         |

|--------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Performance                                      | Slower relative performance where the data rate depends on the processor power and load | Accelerated UDP and TCP/IP from dedicated hardware sustains over 100Mbytes/sec no matter what the system load |

| Power Consumption                                | Higher power requirement due to need for fast processor                                 | Low power hardware solution                                                                                   |

| Modular System BOM Cost                          | Higher system cost through larger CPU and memory requirements                           | Low cost. No CPU needed or a simple embedded CPU or microcontroller can be used for processor functions       |

| Integration Cost                                 | High cost for software design integration and debugging                                 | Low cost, rapid integration, flexible and varied interface options                                            |

| Integration Know-how<br>Needed for System Design | Socket programming/ UDP and TCP/IP protocols/<br>Ethernet standards/ OS                 | Basic understanding of socket programming                                                                     |

#### **Benefits:**

- Low Cost and easy to use with no detailed networking knowledge required

- Offers simple access to very fast data rates over Gigabit Ethernet without having to integrate complex networking hardware and software

- Devices can communicate via Ethernet without using a processor or incurring processor overheads

- Can be quickly and cost-effectively extended to application layer protocols

#### **Features:**

- More than 100MBytes/s sustained data rate in each direction

- High reliability and high stability hardware TOE for UDP and TCP/IP offload

- Single power supply and low external component count

#### **End Markets and Applications:**

- Process Control

- Factory Automation

- Data acquisition

- Storage

- Remote Monitoring and Control Systems

- Machine Vision

Tel +44 1235 838646

# Orange Tree Technologies

| <b>Technical Specification</b> |                                                                                                                                                                                                                                                                      |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Gigabit Ethernet               | Marvell 88E1512 PHY transceiver and Orange Tree's GigEx TCP/IP Offload Engine with 64MBytes DDR SDRAM buffer (48MBytes buffering for network traffic).                                                                                                               |  |

| User Interfaces                | High speed parallel interface to connected user device for data transfer. SPI master, slave and UART interfaces for low speed data transfer.                                                                                                                         |  |

| GigExpedite Protocol Support   | IPv4, TCP, UDP, DHCP Client, Auto IP, UPnP, HTTP, ARP, PTPv2.                                                                                                                                                                                                        |  |

| Real-time Timing Support       | PTPv2 protocol support allowing synchronisation of multiple modules across a network (requires external PTP master clock source). Timed trigger output, event capture and 1 pulseper-second generation. Synchronous Ethernet clock recovery and clock output signal. |  |

| I/O Connectors                 | Two Hirose DF12 connectors carrying interfaces to user devices, MDI connections to Ethernet magnetics and power to the module.                                                                                                                                       |  |

| Flash                          | 256kbytes of Flash dedicated for user web pages                                                                                                                                                                                                                      |  |

| High Speed Interface Clock     | High speed user interface clock rate from 1MHz to 125MHz. Clock can be fed to ZestETM1 from external device or a fixed 125MHz clock can be generated by ZestETM1.                                                                                                    |  |

| Power                          | Single 3.3V input to the board. On-board high efficiency power supplies generate other required voltages. Power consumption less than 1.5W.                                                                                                                          |  |

| Examples                       | C, VHDL and Verilog source code for various examples.                                                                                                                                                                                                                |  |

| Physical                       | 30 x 25 mm                                                                                                                                                                                                                                                           |  |

| Evaluation                     | A breakout board is available to simplify evaluation of the module. The breakout board has an RJ45 connector and connects the user interface of the module to standard 0.1 inch connectors for easy connection to external devices.                                  |  |